Board overview

Front view

# |

Item name |

Description |

|---|---|---|

1 |

SFP2 |

SFP connector |

2 |

SFP2 LEDs |

Connected to the FPGA |

3 |

SFP1 |

SFP connector |

4 |

SFP1 LEDs |

Connected to the FPGA |

5 |

SFP0 |

SFP connector |

6 |

Micro USB port |

See USB-UART. |

7 |

SMA clock output |

J2 SMA connector (see Clocking) |

8 |

SMA clock input |

J1 SMA connector (see Clocking) |

9 |

VHDCI Connector |

J14 - connected to the FPGA (VHDCI0) |

10 |

VHDCI Connector |

J15 - connected to the FPGA (VHDCI1) |

11 |

Blue LED |

Indicates hot-swap state. |

12 |

Green LED |

Indicates Managment CPU activity. |

13 |

FPGA Done LED |

Indicates that the FPGA is programmed. |

14 |

ETH PHY LED1 |

Connected to Ethernet PHY (Activity). |

15 |

ETH PHY LED0 |

Connected to Ethernet PHY (LINK). |

16 |

ETH PHY LED2 |

Connected to Ethernet PHY (MDIO INT). |

LED |

On |

Blinking |

Off |

|---|---|---|---|

Blue |

Ready for hot-swap |

Preparing for hot-swap |

Not ready for hot-swap |

Red |

Power supply error |

N/A |

Power supply ok |

Green |

MMC failure |

Normal operation |

MMC failure |

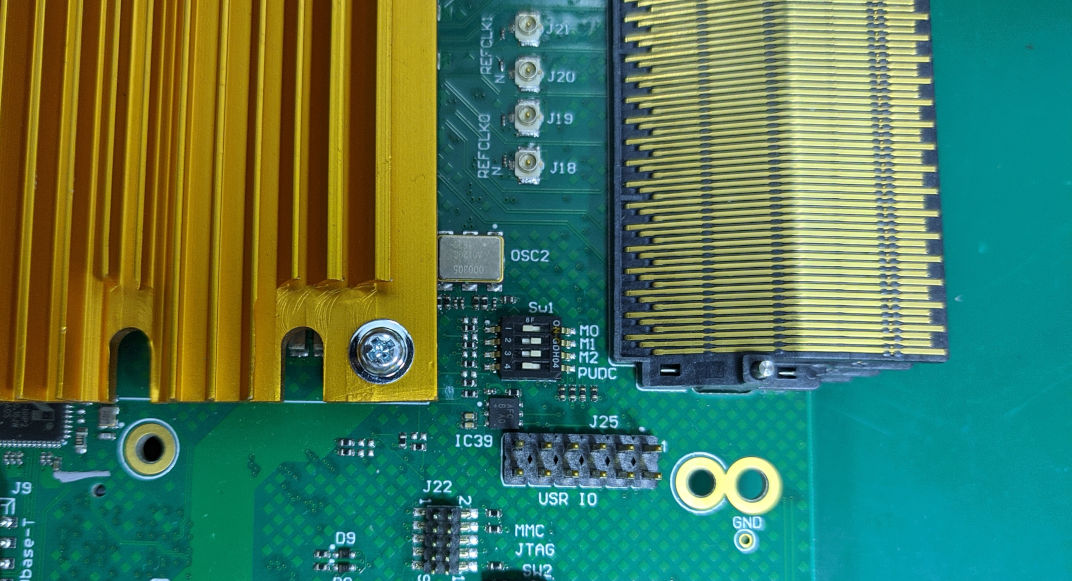

Top view

# |

Item name |

Description |

|---|---|---|

1 |

u.FL connector |

WR helper oscillator output (N/C by default) |

2 |

u.FL connectors |

Clock fanout (IC16) output |

3 |

WR I2C testpoints |

Testpoints of WR Helper (OSC4) oscillator I2C bus. |

4 |

WR I2C testpoints |

Testpoints of WR Main (OSC3) oscillator I2C bus. |

5 |

VHDCI Connector |

J15 - connected to the FPGA (VHDCI1) |

6 |

u.FL connectors |

FPGA MGT bank 224 REFCLK 1 (see Clocking). |

7 |

MCH connector |

Connected to tongue 3 & 4 |

8 |

Clock testpoints |

Testpoints of Si5324 (IC18) clock output |

9 |

u.FL connectors |

FPGA MGT bank 225 REFCLK 1 (see Clocking). |

10 |

FPGA mode switch |

|

11 |

VHDCI Connector |

J14 - connected to the FPGA (VHDCI1) |

12 |

GPIO header |

Connected to the FPGA. See Headers pinout for pinout. |

13 |

FPGA JTAG port |

See JTAG connectors pinout for pinout. |

14 |

Ethernet header |

Connected to Ethernet PHY. See Headers pinout for pinout. |

15 |

CPU JTAG port |

See JTAG connectors pinout for pinout. |

16 |

CPU switch |

Controls CPU operation and upgrade (see Managment CPU). |

17 |

Micro USB port |

See USB-UART. |

18 |

CPU LED |

Indicates CPU power supply |

19 |

SATA port |

J23 (see Transceiver connections) |

20 |

I2C testpoints |

Connected to 4th bus (see I2C connections). |

21 |

MCX clock input |

Alternative to J1 clock input (see Clocking). |

22 |

Exar programmer header |

Header used for programming an optional Exar power module |

23 |

Power module pins |

Pins for an alternative power module with Exar chip. |

24 |

MCX clock input |

J10 - connected to the FPGA (see Clocking). |

25 |

Power supply LEDs |

Indicate state of various power supplies. |

26 |

Power testpoints |

Testpoints connected to various power supplies |

Bottom view

# |

Item name |

Description |

|---|---|---|

1 |

MCH daughterboard connector |

Connects to the MCH |

2 |

SMA clock input |

J1 SMA connector (see Clocking) |

3 |

SMA clock output |

J2 SMA connector (see Clocking) |

4 |

FMC connector |

Used to connect FMC LPC board. See FMC for pinout. |

5 |

SFP0 |

SFP connector |

6 |

SFP1 |

SFP connector |

7 |

SFP2 |

SFP connector |

8 |

Power port |

J5 (see Power supply for pinout) |

Headers pinout

GPIO header - call-out 12 on top view

Ethernet 1000Base-T header - call-out 14 on top view

FPGA boot mode switch

SW1 is used to chose configuration mode of the FPGA. Configuration modes define the specifics of how the FPGA will interact with the data source or external control logic. SW1 is tied directly to Bank 0 of the FPGA. All pins have pull ups, switching SW1 connects the signal to ground. See UltraScale Architecture Configuration User Guide for more information.

M0 |

M1 |

M2 |

Description |

|---|---|---|---|

0 |

0 |

0 |

Master Serial Mode |

0 |

0 |

1 |

Master Parallel Up |

0 |

1 |

1 |

Master Parallel Down |

1 |

0 |

1 |

Peripheral mode |

1 |

1 |

1 |

Slave Serial mode |

SW1 - reccomended settings

Settings shown above (switches 1 and 4 off, 2 and 3 on) allow the FPGA to start up from built-in flash storage.